| Manufacturer: | IME |

| Model: | 86S |

| Year: | 1966 |

| Form: | Desktop |

| Functions: | Basic four, square root, 4 user memories |

| Number of Digits: | 16 |

| Display Type: | Nixie |

| Logic Technology: | DIS |

| Memory Technology: | CORE |

| Diodes: | lots |

| Transistors: | 442 |

| Tech. Data Level: | 3 |

| Tech. Data Source: | MF,RE |

| Tech. Data Pages: | 27+35 |

| Tech. Data: | Schematic, Theory of Operation |

|

The IME 86S was a follow-on to the IME 84.

It is the same physical format and discrete-Ge logic with core memory as the 84,

but takes a big step away from the mechanical-heritage user interface towards a simpler and more intuitive algebraic entry,

and has 3 more user memories.

The core memory in the 86 uses a 2-1/2D,2Wire organisation with a novel use of a charge-pump for power supply to the core.

See the Theory of Operation for more detail.

(Photos & possession / Jef Ongena.)

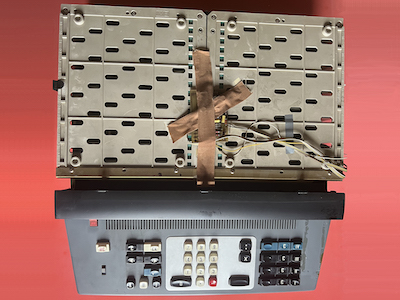

The double card-cage will swing open for access to the backplane.

The small board taped to the top of the card-cage is the 4m modification to adjust the negation behaviour.

|

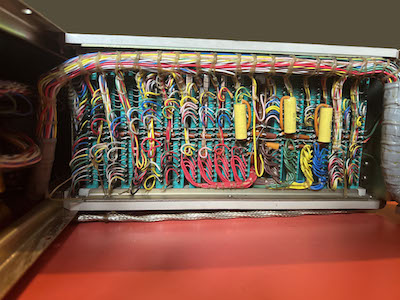

The left half of the hand-wired card-cage backplane.

|

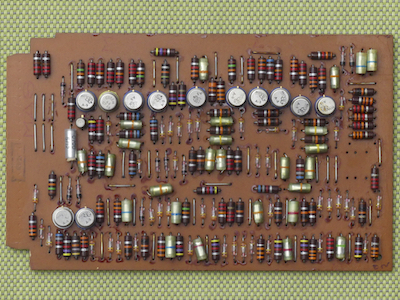

An example of the logic boards.

This is board 3 containing the FKP, FEX, FEEN & FESH flag flip-flops.

|

The core memory as installed in the card-cage.

|

One half of the core memory. This is storage for 2 of the 4 bits of each of the 16 digits of the registers.

This is a 2-1/2D,2Wire scheme.

The horizontal wires are the digit-select lines.

The vertical wires are a combined register-bit select and sense line.

Each vertical column is 1 of the 4 bits of the digits of a register.

While it appears each core has 4 wires going through it, it is actually a double loop of the wire on each axis.

This permitted halving the current requirements from the drivers.

|

ID plate of this unit.

|

- Unit Log -

| Serial Number: | 51409751 |

| Year of Manufacture: | 1966 (sample transistor date codes 6551,6449) |

| Date of Receipt: | 2024 |

| Source: | Remote assistance to J.Ongena. Physical repairs by J.O. |

| State upon Receipt: | Largely functional but hangs on square root and several other faults per repairs of 2024 Sep.

A small board labeled "Minus Logik" is present taped to the top of the card cage and wired to board 4. |

| Date: | 2024 Sep |

| Symptoms: | Several DP neon lamps flickering or not illuminating. |

| Solution: | Replaced. |

| Date: | 2024 Sep |

| Symptoms: | 6th Nixie from right ghosts numerals from other digits. |

| Analysis: | Anode driver does not turn off, likely BC leakage. |

| Solution: | Anode driver replaced with MPSA92. |

| Date: | 2024 Sep |

| Symptoms: | Broken diode on board 3 at ΦPCL input to AND gate feeding 3.12Nv. |

| Solution: | Diode replaced with BAT46. |

| Date: | 2024 Sep |

| Symptoms: | Fractional digit entry with DP at 8 F-Ds enters new numeral at 10^12 digit. |

| Analysis: | - With DP at 8 F-Ds, double pulse occurs on TC=ΦD with the DP entry and then goes away with numeral entry.

This suggests the problem arises during the pulse burst that aligns TC=DP.

During this alignment TC is counting down.

- The double pulses are at TC=8 & TC=12.

- TC comparator gate with ΦDC input is supposed to assert when TC=8 (FTC8=1, FTC4=0, FTC2=0, FTC1=0)

- Conjecture: with the 4~ diode open at gate, that input is 1,

so the gate asserts early, when TC=12 (it thinks FTC4=0 even though it is 1),

and TC alignment stops with TC=12 rather than TC=8.

Diode measures open. |

| Solution: | Diode at 4~ input replaced with BAT46. |

| Date: | 2024 Sep |

| Symptoms: | Pressing square root key hangs the machine. |

| Analysis: | QB signals are persistently active - machine is stuck in QB loop.

F32 is stuck 1, so no 0-edge to terminate QB.

Diode for (I8~=>SG~&SC3=>SK~) input-pair of F32 failed open-circuit. |

| Solution: | Diode replaced with BAT46. |

| Date: | 2024 Sep |

| Symptoms: | Operations to Memory IV produce incorrect results, results from square root are also often incorrect. |

| Analysis: | Square root uses M-IV, so fault is consistent with M-IV problem.

Bit-2 of M-IV is always 0.

Traced to open BC junction of transistor T22.13. |

| Solution: | T22.13 replaced with 2N2907. |

| Date: | 2024 Sep |

| Symptoms: | Accessing M-n for use as an operand leaves the sign of M flipped. |

| Analysis: | FSM stuck 1.

Q~ base gets reset trigger pulse and Q responds by going 0, but state does not hold. |

| Solution: | FSM.Q~ replaced with 2N3906.

FSM now holds states properly and will set and clear on NEG keypresses,

but intended effect is not apparent. |

| Date: | 2024 Sep |

| Symptoms: | Exponentiation results incorrect.

Exponent counter increases by 3, result is often for N+1, e.g. 14^2=>15^2. |

| Analysis: | Inverter 15.10Nv drives GR4INC to increment the exponent count.

If the AND gates driving 15.19Nv had an open input diode,

increments would occur at additional steps where they shouldn't.

Diode at QMC input failed open. |

| Solution: | Diode replaced with BAT46. |

| Date: | 2024 Sep |

| Symptoms: | Overflow occurs on multiplication if DP is at far right (no fractional digits). |

| Analysis: | DP=15 when there are no fractional digits.

This state is explicitly tested for when multiplying by the AND gate feeding 7.1PL.

Diode for F32~ input failed open. |

| Solution: | Diode replaced with BAT46. |

| Date: | 2024 Sep |

| Symptoms: | For first minute or so after power-on, division (and square root) produces incorrect results.

Fault became worse over a few weeks to near-constant. |

| Analysis: | Incrementing of Z, common to both DV & SR, is functioning well.

However testing with n/9 to give same value in quotient digits,

the length of QB1 assertion where subtract-and-increment is performed varies.

This suggests a problem around the FCS & GASUB area producing bad subtractions and bad sign change indications.

Scope shows GASUB signal from inverter 5.10Nd has weak 1-level that decays into the 0/1 transition region. |

| Solution: | T5.10 replaced with 2N3906.

Unit fully functional. |

| Date: | 2024 Oct |

| Symptoms: | Numeral entry does not work. |

| Analysis: | Traced to the FEEN flip-flop.

T3.10.BE open, BC shorted. |

| Solution: | T3.10 replaced with 2N3906.

Unit fully functional. |

| Date: | 2024 Oct |

| Symptoms: | Intermittently, bits do not set 1 in 4th LSD, 8th, 12th.

Those digits often remain 0.

Problem may go away a few minutes after warm up, then return after unit is off for some days. |

| Analysis: | ΦDd which addresses those digits is weak going to 1.

RC curve on rise to -V (1-edge), and sometimes low amplitude.

Something is failing to pull it to -V or something is excessively loading it to GND.

Driving signals for ΦDd gate (ΦDC.1 & ΦDC.2) look good.

Pull-up R for gate OK.

This leaves leaky diode(s) on the many inputs driven by ΦDd as possible culprits. |

| Solution: | Diode for one of the high-side core drivers on board 28 replaced wuth BAT46.

ΦDd signal improved though still some curve on 1-edge.

ΦDd gate-input diode for digit anode driver of 4th LSD (T28.1) shows variability with cold spray.

Diode replaced with BAT46.

ΦDd signal now consistent in shape with other ΦDm. |